Arithmetic Unit (ALU)

ALU memiliki fungsi untuk menerima setiap data biner yang tersimpan dalam memori, kemudian melakukan operasi aritmatika terhadap data tersebut, sesuai dengan instruksi dari Control Unit (CU).

Rangkaian logika dalam ALU merupakan komponen utama yang berfungsi untuk melakukan operasi aritmetika. Rangkaian logika tersebut terdiri atas susunan beberapa gerbang logika (AND, OR, NOT). Rangkaian logika menggunakan Integrated Circuit (IC).

Cara Kerja ALU

Apabila terdapat suatu penjumlahan A + B, maka ALU akan memproses kedua data biner tersebut dengan cara :

- Memori akan mengirimkan data menuju CU. Kemudian, CU akan memulai penjadwalan proses operasi dengan memasukkan nilai A ke accumulator dan B ke b-register.

- Kedua data tersebut kemudian diintruksikan untuk dijumlahkan dalam rangkaian logika oleh CU. Setelah itu, hasilnya dikirimkan kembali ke memori untuk ditampilkan ke dalam peralatan input/output.

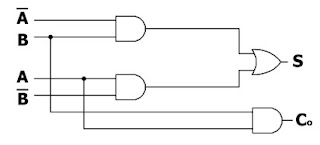

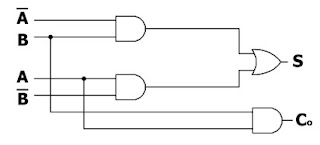

Rangkaian Half Adder

Rangkaian half adder adalah rangkaian logika yang dapat menjumlahkan dua buah input. Half adder akan menghasilkan hasil (sum) serta nilai lebihnya (Carry). Half Adder digunakan sebagai penjumlah dari bit-bit terendah (Least Significant Bit).

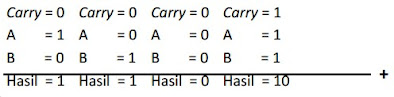

Berikut adalah contoh penjumlahan bilangan biner.

Input dan Output penjumlahan 2 bit biner

|

| Rangkaian Logika Half Adder |

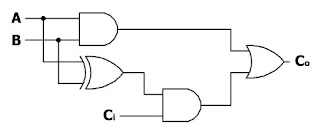

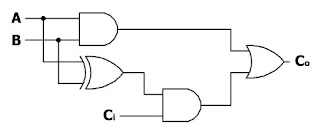

Rangkaian Full Adder

Rangkaian full adder adalah rangkaian logika yang dapat menjumlahkan tiga terminal input dan dua

terminal output. Full adder akan menghasilkan hasil (sum) serta nilai lebihnya (Carry).

|

| Rangkaian Logika S |

|

| Rangkaian Logika C0

|

|

| Input dan Output Rangkaian Full Adder |

Rangkaian Penjumlahan Paralel

Rangkaian penjumlahan paralel digunakan untuk mengoperasikan penjumlahan terhadap dua bilangan dengan nilai bit lebih dari 1. Rangkaian paralel dapat terdiri atas kombinasi beberapa adder.

|

| Rangkaian parallel 2 bit dengan blok Full Adder |

|

| Rangkaian parallel 3 bit |

Jumlah blok yang digunakan dalam rangkaian paralel sesuai dengan jumlah bit bilangan yang dijumlahkan. Untuk mengimplementasikan rangkaian paralel dengan maksimal 4 penjumlahan, dapat digunakan IC 4008 CMOS.

|

| IC 4008 |

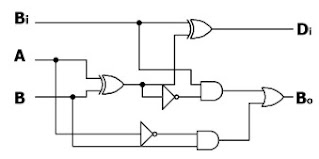

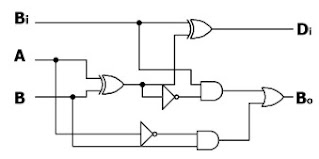

Rangkaian Half Subtractor

Half subtractor adalah rangkaian logika yang digunakan untuk melakukan operasi pengurangan bilangan biner 1 bit. Half Subtractor membutuhkan 2 input serta 2 output. Output yang dihasilkan adalah bit selisih yaitu Difference (Di) dan bit pinjaman yaitu Borrow (Bo)

|

| Input dan Output pengurangan 2 bit biner |

|

| Rangkaian Logika Half Subtractor |

Rangkaian Full Subtractor

Rangkaian full subtractor adalah rangkaian logika yang dapat mengurangi bilangan biner dengan tiga terminal input dan dua terminal output. Full subtractor akan menghasilkan selisih (Difference) serta pinjaman (Borrow).

|

| Rangkaian Full Subtractor |

|

| Input dan Output Rangkaian Full Substractor |

Rangkaian Pengurang Paralel

Rangkaian ini terdiri dari kombinasi rangkaian half substractor dan full substractor untuk melakukan

operasi pengurangan lebih dari 1 bit.

Untuk melakukan pengurangan biner, bilangan input harus diubah menjadi komplemen 2, sehingga dibutuhkan inverter. Rangkaian inverter dapat dibuat dengan menggunakan gerbang XOR.

|

| Rangkaian logika invers dengan XOR |

Selain inverter, dibutuhkan rangkaian untuk mengubah input menjadi bentuk komplemen 2. Rangkaian ini membutuhkan half adder dan full adder yang dikombinasikan dengan rangkain XOR sebelumnya.

|

| Rangkaian logika invers dengan XOR |

|

| Bentuk akhir rangkaian setelah ditambahkan komponen input dan output |

Posting Komentar untuk "Arithmetic Logic Unit"